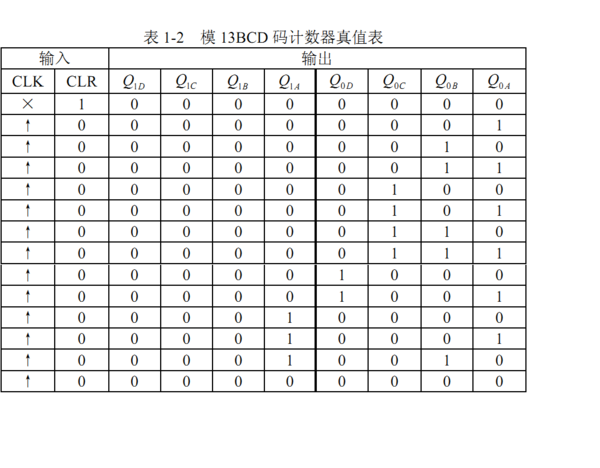

FPGA 数电 如何用74160加法计数器 实现 模13BCD码计数器 模13BCD码计数器的真值表如图示

FPGA 数电 如何用74160加法计数器 实现 模13BCD码计数器 模13BCD码计数器的真值表如图示

用T触发器设计一个带进位标志的余3BCD码同步加法计数器.

74161集成计数器功能真值表如下表所示,其惯用符号如下图所示,用置数端LD实现从0000-1001的十进制计数器

74LS160计数器的逻辑符号如题下图所示,画出用它实现模6计数器的电路图

用Verilog HDL设计一个4位BCD码计数器

如何用74LS161制成60进制的计数器?

64位移位寄存器最多可实现模为多少的环行计数器及扭环形计数器

一道数字电路题,用T触发器设计一个带进位标志的余3BCD码同步加法计数器,要求列出状态表,求出电路的驱动方程和输出方程.

如何用同步十进制双时钟可逆计数器74LS192构成16进制的可逆计数器

请问:如何用集成计数器74LS161设计一个五进制计数器?试题,

如何用74ls161实现23进制计数器要用同步级联,反馈清零法

BCD码计数器初值低八位范围是多少,高八位范围是多少?